Lattice Semiconductor正在挑战英特尔和Xilinx FPGAs的低端产品,其最高密度的器件拥有多达100,000个逻辑单元和更高性能的I/O。Certus Pro-NX系列拥有40,000个逻辑单元,

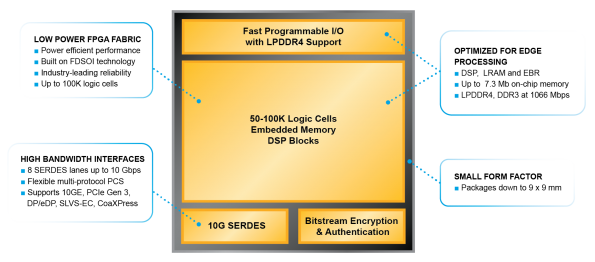

Lattice Semiconductor正在挑战英特尔和Xilinx FPGAs的低端产品,其最高密度的器件拥有多达100,000个逻辑单元和更高性能的I/O。

Certus Pro-NX系列拥有40,000个逻辑单元,并提供10Gbit/s以太网和第3代PCIe接口。

Lattice Semiconductor的产品营销经理JuJu Joyce表示:“Pro-NX的起点是50,000个逻辑单元,因此它的目标是下一个级别。Pro-NX将于明年下半年开始批量出货,此前该公司已于明年上半年推出其下一代FPGA技术Nexus5。

Nexus5 FPGA将基于与当前一代相同的28纳米FD-SOI CMOS工艺技术构建,这将限制增加单元数量的能力。

“我们的目标一直是保持价格竞争力,但我们提供更多的价值,”乔伊斯说。“我们发现,在部署了许多边缘网络的恶劣环境中,在蜂窝基站或没有电机控制气流的环境中,或者在小型工业摄像机模块中,需要低功耗来实现更简单的热管理。他说:“专为这一级别的汽车打造,你可以获得更高的能效。”

“随着各种传感器在边缘产生更多数据,需要更高的带宽,这些传感器的能力越来越强,分辨率越来越高,”他说。

I/O为低功耗LPDDR4内存接口提供强化IP,为8通道SERDES和第三代PCIe或10G以太网连接提供10.3Gbit/s。它还包括用于传感器、Coaxpress和DisplayPort的SLVS-EC。

该系列设备还包括高达7.3兆位的片内存储器,以支持机器学习框架,而不必离开芯片。

乔伊斯说:“人工智能推理的一个瓶颈是片上内存,用于存储神经网络的权重,为了克服这一瓶颈,我们提供了65%的片上内存,因此对于许多处理功能,你不必依赖增加额外延迟和功率的外部存储器。”“我们在结构中的列中有18k位的EBR嵌入式块RAM,我们有512k位的大型RAM块,这些块位于通过标准结构连接的外围设备上。”-

具有最低密度接口的最小器件适合采用9 x 9 mm BGA封装,球距为0.5mm,紧密集成,额定温度范围为-40至+125C,适合工业应用。

各种人工智能和机器视觉堆栈将被移植到新设备上,并且有一个更新版本的Radiant设计工具。

Radiant 3.0中的SERDES分析工具得到了增强,以适应CertusPro-NX器件支持的更高SERDES带宽,并且通过图形用户界面(GUI)改善了整个设计流程中的信号可追溯性,以帮助设计人员跟踪HDL源到RTL视图以及技术视图之间的信号。

Radiant还允许用户在晶格合成引擎(LSE)和Synplify Pro合成引擎之间进行选择。在Radiant 3.0中,时序约束和时序分析在两个合成引擎中是统一的。时序分析已经从其他操作中分离出来,因此它可以独立运行,通过帮助设计人员评估“假设”场景和重新运行时序分析来加速迭代设计过程,而不必重新运行映射和布局布线。

“Lattice Radiant 3.0设计软件为开发者提供了易于遵循的用户体验;该工具引导他们完成开发流程的各个步骤,包括设计创建、导入IP、实施、比特流生成、将比特流下载到FPGA以及调试,”Lattice Semiconductor软件高级产品线经理Roger Do说道。

“几乎没有或完全没有FPGAs工作经验的开发人员可以快速利用Lattice Radiant的自动化功能。对于有经验的FPGA开发人员来说,如果需要特定的优化,Lattice Radiant 3.0允许对FPGA设置进行更细粒度的控制,”他说。